目前流行的ARM芯片內(nèi)核有ARM7TDMI、ARM720T、ARM9TDMI、ARM992T、ARM940T、ARM946T、ARM966T和ARM10TDMI等,Philips LPC2214是基于ARM7TDMI-S的高性能32位RISC微控制器,它集成了Thumb擴(kuò)展指令集,256KB可在系統(tǒng)中編程的片內(nèi)Flash和可在應(yīng)用中編程的16位KB RAM,向量中斷控制器,外部總線控制器,2個UART,I2C串行接口,2個SPI串行接口,2個定時器(7個捕獲/比較通道),可提供多達(dá)6個PWM輸出的PWM單元,8通道10位ADC,實時時鐘,看門狗定電感線圈時器以及112個通用I/O引腳,通過可編程的片內(nèi)鎖相環(huán)(PLL)可實現(xiàn)LPC2214最高為60MHz的CPU時鐘頻率,相對眾多ARM系列產(chǎn)品來說,Philips公司生產(chǎn)的LPC2214是一款性價比較高的ARM7芯片。

嵌入式實時操作系統(tǒng)有助于提高系統(tǒng)可靠性和開發(fā)效率,且能夠充分發(fā)揮32位CPU的多任務(wù)處理能力,常見的嵌入式操作系統(tǒng)有Linux、Windows CE、VxWorks、Nucleus、uC/OS-II等,其中uC/OS-II是一個可移植、可固化、可裁剪的占先式實時操作系統(tǒng),其周邊的配套產(chǎn)品也比較完善,如uC/FS,uC/GUI等產(chǎn)品都為其應(yīng)用增強了適用性,相對其他操作系統(tǒng)而言,uC/OS-II正常運行只需十幾或幾十KB的Flash空間和SRAM空間,并且其所需的授權(quán)費用也相對較低,結(jié)合以LPC2214為核心的硬件平臺,在這里采用了uC/OS-II作為該設(shè)備的嵌入式操作系統(tǒng)。

有上述分析可知,選擇LPC2214和uC/OS-II相結(jié)大電流功率電感器工廠合的嵌入式平臺是一種較為經(jīng)濟(jì)而實用的方法。

2 音頻解碼芯片的選擇

LPC2214與uC/OS-II相結(jié)合的平臺有比較強大的處理能力,但在許多應(yīng)用場合中仍顯不足,在本文所介紹的應(yīng)用中,系統(tǒng)需要具有音頻編解碼功能,音頻的編解碼方式包括軟件編解碼和硬件編解碼,如果采用軟件編解碼的方式,最對處理器的處理速度要求一般在50MIPS以上,而LPC2214的處理速度僅有70MIPS左右,顯然倘若采用這種方式,LPC2214處理能力將受到很大限制,所以,采用專門的音頻處理芯片來處理音頻數(shù)據(jù)對該平臺的來說是個正確的選擇,這里選用一款性能優(yōu)越的音頻解碼芯片--VS1003。

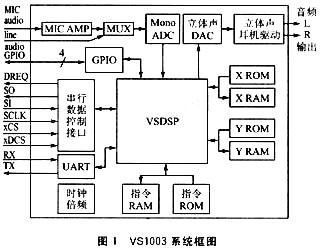

VS1003音頻解碼芯片為VS10XX系列的第三代產(chǎn)品,是芬蘭VLSI Solution Oy公司生產(chǎn)的單片MP3/WMA/MIDI解碼和ADPCM編碼芯片,它內(nèi)部包含一個高性能、低功耗的DSP處理核(VSDSP),一個工作內(nèi)存,一片可供用戶程序使用的5.5KB RAM,一個串行SPI總線接口,一個高質(zhì)量的采樣頻率可調(diào)的過采樣DAC以及一個16位的采樣ADC,VS1003的內(nèi)部構(gòu)造如圖1所示。

3 VS1003控制協(xié)議的實現(xiàn)

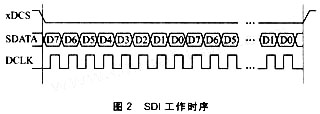

VS1003通過一個工作于從模式的SPI串行總線與主機進(jìn)行數(shù)據(jù)和控制信息的交流,音頻數(shù)據(jù)通過串行數(shù)據(jù)接口(SDI)傳送,控制數(shù)據(jù)則通過串行控制接口(SCI)來傳送,控制數(shù)據(jù)總是為16位,通過讀/寫不同的寄存器來實現(xiàn)對VS1003的控制。

VS1003的SPI接口具有兩種工作模式:VS1002新模式和VS1001兼容模式。設(shè)置SM_SDINEW為1,使VS1003處于VS1002新模式。當(dāng)SMSDISHARED為0時,控制信號和數(shù)據(jù)信號的傳送分別采用xCS和xDCS作為同步信號,而當(dāng)SMSDISHARED為1時,共用xCS作為同步信號,設(shè)置SM_SDINEW為0,使VS1003處于VS1001兼容模式,該模式僅以xCS作用同步信號。

作為從機工作模式,VS1003通過一個信號線DREQ指示是否允許主機傳送數(shù)據(jù),當(dāng)DREQ為高時,VS1003至少可以接受32KB的SDI數(shù)據(jù)或者SCI控制命令。

在這里,以VS1002新模式且SMSDISHARED設(shè)置為0為例介紹VS1003通信協(xié)議的實現(xiàn)。圖2描述了SDI工作時序,它以xDCS為同步信號,隨著時鐘信號DCLK的變化,數(shù)據(jù)根據(jù)SCL_MODE的設(shè)置依次從高位或低位送出。

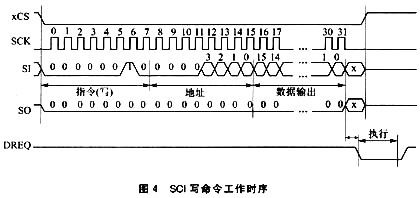

SCI協(xié)議包括1個控制指令字節(jié)、1個地址字節(jié)和1個16位數(shù)據(jù)字。每次讀寫控制可以操作一個寄存器。讀命令和寫命令分別為0x03和0x02,這兩種控制命令的工作時序分別如圖3和圖4所示。

4 電路設(shè)計

本設(shè)計最終要實現(xiàn)的目標(biāo)是一款具有人機界面及數(shù)據(jù)存儲功能的工控手持設(shè)備,通過人機對話界面發(fā)送控制命令來操縱VS1003,以實現(xiàn)錄放音功能。

4.1 硬件電路設(shè)計

VS1003的所有數(shù)據(jù)和控制命令均通過SPI總線接口實現(xiàn),因此與LPC2214的接口實現(xiàn)比較簡單,包括3條SPI數(shù)據(jù)線和4條控制線,如圖5所示。 大功率電感廠家 |大電流電感工廠