圖像傳感器,是組成數(shù)字攝像頭的重要組成部分。如果沒有傳感器,就沒有圖像信號可進行處理。眾所周知傳感器是非標準化的。在采用的方案中,它們有以下的不同之處:

轉(zhuǎn)換可見光或紅外光為電信號的方式;尤其是在該信號離開這塊芯片之前,對這個信號采用的編碼和壓縮(有時)的方式。

對傳感器內(nèi)部的寄存器進行編程的方式,以調(diào)整增益、曝光時間、傳感器模式(如線性、HDR),傳感器圖像坐標等。

實現(xiàn)特殊功能的方式,如高(或?qū)挘﹦討B(tài)范圍(HDR/WDR);例如通過在同一封裝中的多個傳感器,對于同一圖像幀多次曝光等。

這些傳感器廠商采用的接口,以使這些電子圖像信號離開傳感器,并進入下游的處理邏輯。

FPGA提供一個具成本效益的,尺寸非常小的可編程邏輯平臺,可以輕松地將信號從不同的圖像傳感器接口轉(zhuǎn)換到數(shù)字信號,以供下游的邏輯進行處理。FPGA提供具有成本效益的可編程機制,以適應(yīng)各種信號編碼方案、寄存器管理方案和傳感器接口,從而為不同類型的傳感器提供可編程支持。

圖像傳感器技術(shù)

根據(jù)用于將可見塑封電感光轉(zhuǎn)換成電信號的基本技術(shù),圖像傳感器可分為兩大類。它們是CCD(電荷耦合器件)傳感器和CMOS(互補金屬氧化物半導(dǎo)體)傳感器。到目前為止,出貨量最多的圖像傳感器是CMOS傳感器。本文只關(guān)模壓電感注CMOS傳感器接口。

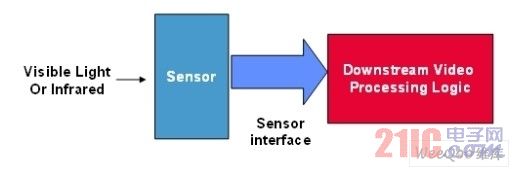

在視頻處理鏈中典型的圖像傳感器的應(yīng)用如圖1所示。

圖1 在視頻處理鏈中典型的圖像傳感器的應(yīng)用

如今有幾個著名的圖像傳感器制造商,它們是Aptina、OmniVision Technologies、索尼、三星、松下、東芝和Altasens。

如前所述,傳感器制造商配置了一系列接口,用于將離開其芯片的圖像信號傳至下游邏輯進行處理。非常普遍的是,同一傳感器制造商根據(jù)需要從芯片中提取的數(shù)據(jù)量使用不同的接口。例如,具有兆像素分辨率的現(xiàn)代傳感器需要在給定的周期時間傳出比僅具有VGA級分辨率的傳感器多得多的數(shù)據(jù)。像高動態(tài)范圍(HDR)這樣的要求還增加了數(shù)據(jù)量,需要從每個圖像幀的圖像傳感器讀取數(shù)據(jù),而為支持平滑、低延遲高品質(zhì)的視頻,需要在給定的時間內(nèi)從傳感器芯片提取幀數(shù),這也影響了傳感器接口的選擇。

圖像傳感器接口的演進

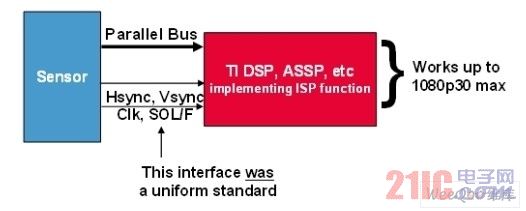

到目前為止,所有傳感器都可連接到并行LVCMOS接口,如圖2所示。傳感器電感廠家分辨率和幀速率已經(jīng)提高到一個水平,此時以前的主流CMOS并行接口已不能處理所要求的帶寬。

圖2 并行LVCMOS圖像傳感器I/F

由于兆像素傳感器的問世,對更高電感生產(chǎn)速度的需求激增,HDR和對支持更高幀速率、新型、更高速度傳感器的需求正使用不同的接口來克服并行LVCMOS的局限性。例如,索尼和松下使用并行的子LVDS接口,OmniVision使用MIPI或串行LVDS。另一個例子是,為支持更高帶寬的需求,Aptina Imaging已經(jīng)推出了稱為HiSPi(高速串行像素接口)的高速串行接口。HiSPi接口可以工作在1-4個串行數(shù)據(jù)通道,加上1個時鐘通道。每個信號是子LVDS差分信號,以 0.9V的共模電壓為中心。每個通道可以運行在高達700Mbps下。

HiSPi與并行傳感器接口橋接的需求

多個傳感器接口給標準化下游視頻處理環(huán)型電感器邏輯的制造商提出了一個問題,因為用一個ASSP支持許多不同的傳感器接口非常困難。

大多數(shù)ISP(圖像信號處理)器件支持傳統(tǒng)的CMOS并行傳感器接口,但通常缺乏對高速串行接口的支持。很多ISP并行接口的運行速度遠遠超過了傳感器的并行接口。但是,由于傳感器已遷移到不同串行接口,ISP器件需要邏輯以轉(zhuǎn)換到并行接口。因此FPGA橋接器件需要將高速串行數(shù)據(jù)轉(zhuǎn)換到并行格式。對于視頻信號處理ASSP的制造商(他們擁有支持更快的并行CMOS傳感器接口的現(xiàn)成產(chǎn)品),F(xiàn)PGA解決了連接至高速串行傳感器的問題。FPGA提供在高速傳感器和傳統(tǒng)圖像信號處理ASSP之間的簡單、具有成本效益的可編程橋接。這個概念如圖3所示。 大功率電感廠家 |大電流電感工廠