摘要 基于直接數(shù)字頻率合成技術(shù)的思想,采用現(xiàn)代數(shù)字信號(hào)處理和顯示技術(shù),設(shè)計(jì)了一臺(tái)低成本、數(shù)字化、智能化的頻率特性測試儀。實(shí)現(xiàn)了對(duì)20 Hz~150 MHz范圍內(nèi)任意頻段的被測網(wǎng)絡(luò)幅頻特性和相頻特性測量。完成了數(shù)據(jù)存儲(chǔ)、-3曲帶寬計(jì)算、峰值查找等功能,幅度檢測精度達(dá)到1dBm,相位檢測精度1°等指標(biāo)。

關(guān)鍵詞 DSP;DDS;幅頻測量;相頻測量

傳統(tǒng)掃頻儀的信號(hào)源大多采用LC電路構(gòu)成的振蕩器,大量使用分立元器件來實(shí)現(xiàn)各功能,顯示部分采用傳統(tǒng)的掃描顯示器。因此傳統(tǒng)結(jié)構(gòu)的掃頻儀不僅結(jié)構(gòu)復(fù)雜、體積龐大、價(jià)格昂貴、操作復(fù)雜,而且由于各元件分散性大,參數(shù)變化容易受外部環(huán)境變化影響,精度不高。目前,以Agilent等為代表的儀器生產(chǎn)廠家提供了多種高性能的共模電感器頻率特性測試儀。但其產(chǎn)品主要集中在射頻、微波等高頻領(lǐng)域,中低頻段的產(chǎn)品相對(duì)缺乏。本文基于直接數(shù)字頻率合成(DDS)的技術(shù)思想,采用DSP和FPGA架構(gòu)的現(xiàn)代數(shù)字信號(hào)處理技術(shù),設(shè)計(jì)了一臺(tái)低成本,高度數(shù)字化和智能化的頻率特性測試儀,實(shí)現(xiàn)了對(duì)20 Hz~150 MHz范圍內(nèi)任意頻段的被測網(wǎng)絡(luò)幅頻特性和相頻特性測量和顯示,完成了數(shù)據(jù)存儲(chǔ)回放和傳輸,-3 dB帶寬計(jì)算,峰值查找等功能。幅工字電感器度檢測精度達(dá)到1dBm,相位檢測精度1°的指標(biāo)。

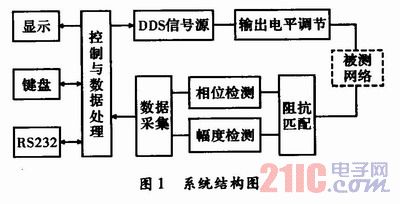

1 系統(tǒng)組成

頻率特性分析儀主要包括控制和數(shù)據(jù)存儲(chǔ)處理單元、DDS信號(hào)源單元、幅度和相位檢測單元、數(shù)據(jù)采集單元、顯示及交互接口單元,系統(tǒng)總體框圖如圖1所示。

2 系統(tǒng)設(shè)計(jì)

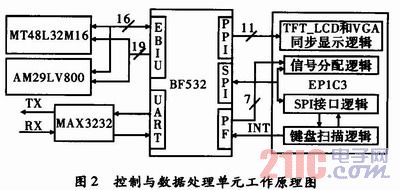

2.1 控制與數(shù)據(jù)處理單元

ADSP—BF532和FPGA(EP1C3)共模電感器是控制與數(shù)據(jù)存儲(chǔ)處理單元的核心。DSP通過PPI、SPI和PF接口與FPGA進(jìn)行雙向數(shù)據(jù)通信,實(shí)現(xiàn)鍵盤讀取,DDS掃描,A/D采集,LCD掃描等功能,通過UART單元與計(jì)算機(jī)實(shí)現(xiàn)數(shù)據(jù)傳輸和遠(yuǎn)程控制。FPGA完成了TFT_LCD和VGA同步顯示時(shí)序轉(zhuǎn)換、鍵盤掃描、SPI通信和信號(hào)分配等功能。另外,DSP通過EBIU單元連接AM29LV800和MT48L32M16分別作為程序與工作狀態(tài)存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)與顯示緩存。工作原理如圖2所示。

2.2 數(shù)據(jù)采集單元

數(shù)據(jù)采集單元采用多路A/D轉(zhuǎn)換器將幅度和相位的模擬電壓信號(hào)轉(zhuǎn)換為數(shù)字信號(hào)供DSP和FPGA進(jìn)行處理和傳輸,是模擬電路和數(shù)字電路之間的“橋梁”。本儀器中選用AD7655采集信號(hào)。該A/D轉(zhuǎn)換器具有4個(gè)模擬輸入通道,16位采樣精度,最高采樣率為1MHz。采用16位并行和SPI等傳輸模式。REF3125提供A/D轉(zhuǎn)換器所需的2.5 V參考電壓。

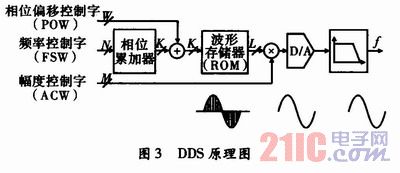

2.3 DDS信號(hào)源單元

DDS技術(shù)是一種把一系列數(shù)字量形式的信號(hào)通過DAC轉(zhuǎn)換成模擬量形式信號(hào)的合成技術(shù)。DDS技術(shù)建立在采樣定理的基礎(chǔ)上,它首先對(duì)需要產(chǎn)生的波形進(jìn)行采樣,將采樣值數(shù)字化后存入存儲(chǔ)器做為查找表,然后再通過查找表將數(shù)據(jù)讀出,經(jīng)過D/A轉(zhuǎn)換器轉(zhuǎn)換成模擬量,把存入的波形重新合成出來。雖然DDS系統(tǒng)的結(jié)構(gòu)有很多種,但其基本的電路原理,如圖3所示。

電感器類型 本儀器選用的DDS芯片AD9958是一款高性能雙通道直接數(shù)字頻率合成器,具有兩個(gè)獨(dú)立的DDS核,分別具有兩個(gè)獨(dú)立的32位頻率控制字和14位相位控制字,一個(gè)10位的幅度控制字。內(nèi)部集成PLL,芯片最高工作頻率500 MHz,輸出信號(hào)最高頻率可達(dá)180 MHz。DSP通過SPI和PF接口經(jīng)FPGA信號(hào)分配邏輯對(duì)AD9958進(jìn)行頻率、相位和幅度控制字的配置,如圖4所示。

AD9958采用25 MHz外部時(shí)鐘輸入,經(jīng)內(nèi)部PLL倍頻后產(chǎn)生500 MHz內(nèi)核工作時(shí)鐘。輸出信號(hào)為兩路同頻的正弦和余弦信號(hào)。為避免數(shù)字噪聲對(duì)信號(hào)產(chǎn)生干擾,芯片的3.3 V數(shù)字供電與模擬供電部分需采用型網(wǎng)絡(luò)隔離,并對(duì)模擬地接小電阻到地平面以隔共模電感離干擾。由于芯片輸出為電流信號(hào),需采用51Ω上拉到1.8 V轉(zhuǎn)換為電壓信號(hào),經(jīng)LFCN—160集成濾波器濾除高頻噪聲,并采用差分運(yùn)放AD8312抵消共模噪聲。輸出信號(hào)電平范圍為-10~-3 dBm。AD9958信號(hào)輸出原理如圖5所示。 大功率電感廠家 |大電流電感工廠