1前言

印制電路板(PCB)信號完整性是近年來熱議的一個話題,國內已有很多的研究報道對PCB信號完整性的影響因素進行分析,但對信號損耗的測試技術的現狀介紹較為少見。

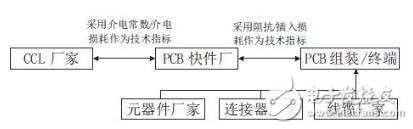

PCB傳輸線信號損耗來源為材料的導體損耗和介質損耗,同時也受到銅箔電阻、銅箔粗糙度、輻射損耗、阻抗不匹配、串擾等因素影響。在供應鏈上,覆銅板(CCL)廠家與PCB快件廠的驗收指標采用介電常數和介質損耗;而PCB快件廠與終端之間的指標通常采用阻抗和插入損耗,如圖1所示。

圖1 PCB材料及組裝的部分技術指標

針對高速PCB設計和使用,如何快速、有效地測量PCB傳輸線信號損耗,對于PCB設計參數的設定和仿真調試和生產過程的控制具有重要意義。

2 PCB插入損耗測試技術的現狀

目前業界使用的PCB信號損耗測試方法從使用的儀器進行分類,可分為兩大類:基于時域或基于頻域。時域測試儀器為時域反射計(Time DomainReflectometry,簡稱TDR)或時域傳輸計(TimeDomain Transmission,簡稱TDT);頻域測試儀器為矢量網絡分析儀(Vector Network Analyzer,簡稱VNA)。在IPC-TM650試驗規范中,推薦了5種試驗方法用于PCB信號損耗的測試:頻域法、有效帶寬法、根脈沖能量法、短脈沖傳播法、單端TDR差分插入損耗法。

2.1頻域法

頻域法(Frequency Domain Method)主要使用矢量網絡分析儀測量傳輸線的S參數,直接讀取插入損耗值,然后在特定頻率范圍內(如1 GHz ~ 5 GHz)用平均插入損耗的擬合斜率來衡量板材合格/不合格。 大功率電感廠家 |大電流電感工廠